Intel Alder Lake: Todo sobre la Arquitectura, Núcleos y Rendimiento

por Mikel Aguirre Actualizado: 25/08/2021 9Introducción

Ya queda menos para que veamos en el mercado la tan esperada arquitectura Intel Alder Lake. Así nos lo ha hecho saber Intel en una presentación sobre sus características técnicas en la que hemos estado presentes y cuyos detalles os desvelamos y detallamos en este artículo. En enero de 2021 Intel mostró un prototipo funcionando en un vídeo difundido con motivo del CES.

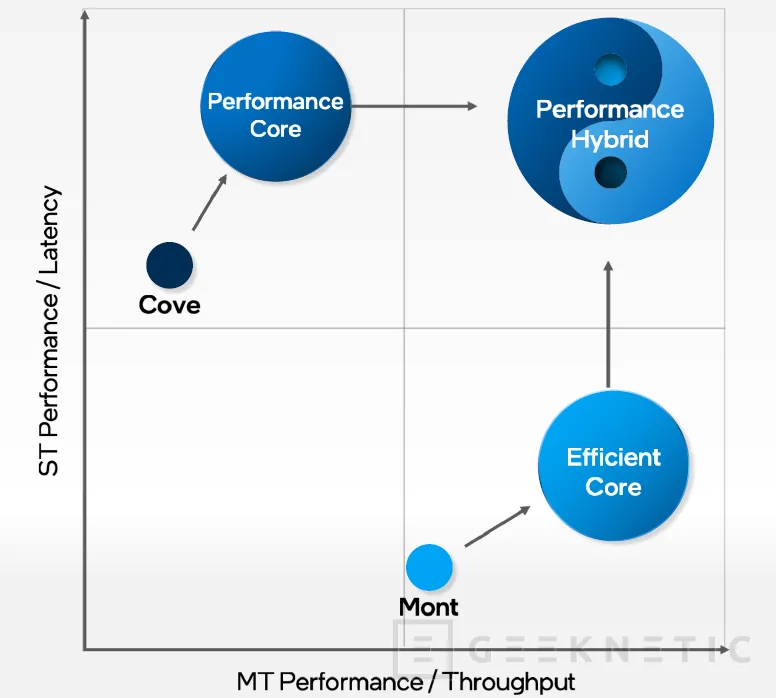

Según sabemos desde hace tiempo, la principal característica que introducirá Intel con Alder Lake es un diseño basado en una configuración de núcleos big.LITTLE, que hasta ahora solo habíamos visto en segmentos como los smartphones y similares.

No es la primera vez que Intel prueba algo similar; sus procesadores de portátil con nombre en clave Lakefield estaban compuestos de un núcleo grande (Sunny Cove) y 4 núcleos pequeños (Tremont). La diferencia es que ahora Intel está llevando la configuración big.LITTLE a todo su portfolio de soluciones, desde sobremesas de alto rendimiento para gaming a portátiles de todo tipo y por supuesto servidores.

Hoy por fin conocemos los nombres y los detalles de los 2 tipos de núcleos que componen la arquitectura. Se trata de los “Performance Cores” con nombre en clave Golden Cove y los “Efficient Cores” con nombre en clave Grace Mont. Son 2 tipos de microarquitecturas diferentes funcionando de forma concurrente en una misma CPU y adaptándose a las necesidades computacionales de cada momento. Un nuevo modelo de computación híbrida para todo tipo de productos.

El hecho de disponer de distintos tipos de núcleos en una misma CPU supone un cambio fundamental en la forma en la que el sistema operativo debe gestionar los hilos. Para solucionarlo Intel ha desarrollado una tecnología que llaman “Thread Director” (director de hilos) que va integrada en el propio procesador.

En las siguientes secciones os detallamos las características principales de Alder Lake, cada tipo de núcleo, su rendimiento, el funcionamiento de su nuevo “Thread Director” y las CPUs que podemos esperar basadas en esta arquitectura.

Características Principales de Alder Lake

Aparte del cambio a big.LITTLE, Alder Lake introducirá ciertas grandes mejoras en cuanto a sus características, interfaces y conectividad.

Proceso de fabricación de Alder Lake

Está fabricado en el nuevo proceso Intel 7. Recordemos que Intel ha realizado recientemente un cambio de nomenclatura en sus procesos de fabricación y lo que antes se conocía como 10nm Enhanced SuperFin ahora se conoce como Intel 7. Este proceso es al final una evolución del proceso de 10nm SuperFin y supone una mejora de un 10-15% de rendimiento por vatio.

TDP Configurable

Recordemos que Alder Lake se va a implementar en todos los segmentos. Tendremos CPUs de portátil de alto rendimiernto, CPUs de portátil de bajo consumo, CPUs de Sobremesa y CPUs de servidor. Aunque Intel no ha detallado que TDPs tendrá cada producto ni cada gama, sí que han desvelado que van en total desde los 9W hasta los 125W en productos de consumo.

Podemos deducir por tanto que en portátiles de bajo consumo podremos ver configuraciones de TDP que parten de los 9W. En sobremesas veremos CPUs con un TDP de hasta 125W.

Por el momento no tenemos información de modelos específicos pero estos 125W máximos coinciden con el TDP especificado para el Core i9-11900K basado en Rocket Lake, podemos hacernos a la idea de que al menos en sobremesa seguirán la misma línea, y un supuesto Core i9-12900K también tendrá este TDP.

Memoria RAM

Alder Lake es la primera arquitectura de Intel en introducir soporte completo para DDR5 y LP5 desde el primer momento. No obstante nos han asegurado, que seguirá habiendo soporte para DDR4. Otra cosa será qué implementación hagan los fabricantes de placas base.

Estos son todos los interfaces de memoria soportados y sus frecuencias máximas.

- DDR5-4800

- DDR4-3200

- LP5-5200

- LP4x-4266

Mantenemos el máximo de 3200MHz para DDR4 y tenemos 4800MHz en DDR5. Intel nos explica que mejorarán el soporte para overclock the memoria en esta arquitectura, y aunque no lo han mencionado, es suficiente razón para dar por hecho que seguiremos disponiendo de perfiles XMP en sobremesa, además de los de la JEDEC.

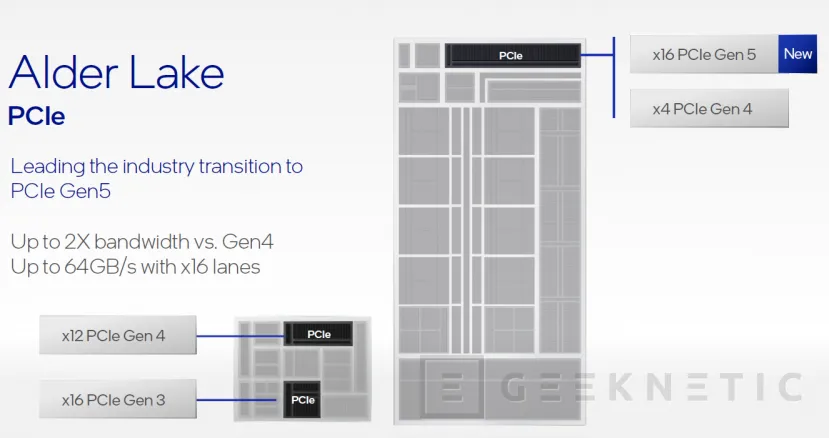

Interfaces PCI-Express

Si bien AMD se adelantó a Intel en la implementación del PCI-Express de 4ª generación, en este caso podemos contar con que Alder Lake soportará de forma nativa PCIe de 5ª generación.

El soporte máximo de líneas PCIe, que entendemos, se refiere al tope de gama en sobremesa, es el siguiente:

- 16 Líneas PCIe Gen5 en la CPU

- 4 Líneas PCIe Gen4 en la CPU

- 12 Líneas PCIe Gen4 en el chipset

- 16 Líneas PCie Gen3 en el chipset

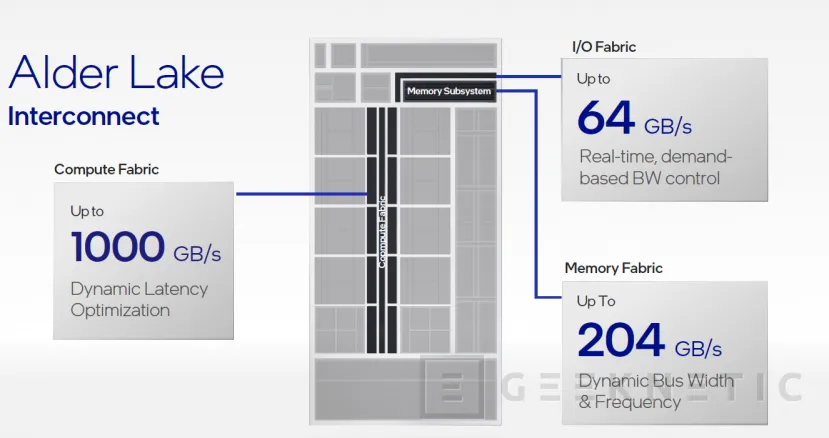

Interconnect

Intel ha mejorado los enlaces que conectan los núcleos entre sí, con el interfaz de memoria y el resto de las interfaces. Según indican obtienen una optimización de latencia dinámica de hasta 1.000GB/s.

El acceso a memoria es de hasta 204GB/s con una gestión dinámica del ancho de banda y la frecuencia. El acceso al resto de interfaces de entrada/salida es de hasta 64GB/s con un control de ancho de banda bajo demanda en tiempo real.

Thunderbolt y Wi-Fi 6

Los equipos basados en Alder Lake también soportarán Wi-Fi 6E y Thunderbolt 4 aunque su implementación dependerá de otros factores como disponer del puerto necesario, el chip para Wi-Fi elegido por el fabricante de la placa o del portátil en cada caso, etc.

Nuevo Socket LGA 1700

Aunque Intel ya lo ha mencionado en otras ocasiones, se reafirman el cambio de socket para sobremesa. Si queremos hacer funcionar una CPU de sobremesa 12ª generación (nombre que falta confirmar) necesitaremos una placa base con el nuevo socket LGA 1700.

Aunque siempre es un fastidio no poder disfrutar de una nueva CPU con tu placa actual, lo cierto es que el cambio en el producto con la introducción de la arquitectura big.LITTLE hace obvia la necesidad de cambiar de socket para poder soportarlo. De hecho, estamos ante un incremento de 500 pines con respecto al socket LGA 1200 que están a punto de jubilar.

El socket es además 7,5mm más largo por lo que lo hace incompatible con las soluciones de refrigeración actuales. Es posible que algunos fabricantes de soluciones de refrigeración saquen adaptadores o clips de ajuste para hacer compatibles sus productos con este nuevo socket mientras esperamos a que saquen nuevos sistemas de refrigeración que lo soporten de forma nativa.

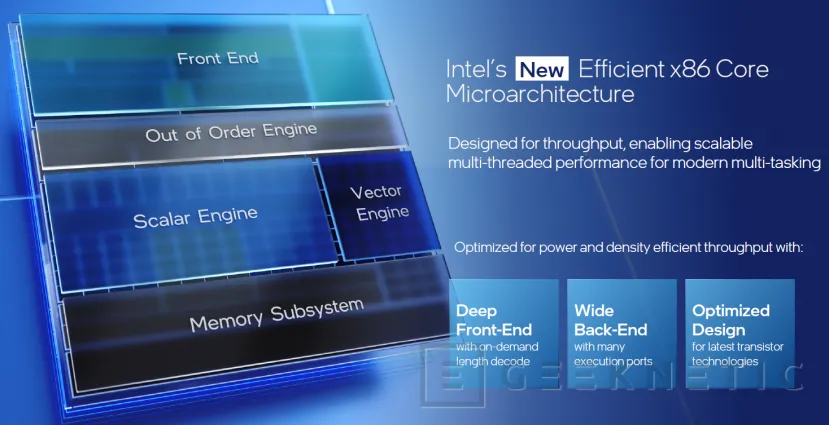

Intel Efficient Core – Microarquitectura Grace Mont

Esta microarquitectura está destinada a la eficiencia y por tanto a tareas que no requieren de un gran rendimiento. Su finalidad principal es ejecutar procesos de la forma más eficiente posible de forma que ahorremos energía y necesidades de disipación.

Los “Efficient Cores” se agrupan siempre en conjuntos de 4 núcleos, y no disponen de hyperthreading. Una CPU que tenga, por ejemplo, 8 núcleos de este tipo tendrá por tanto capacidad para ejecutar 8 hilos de forma concurrente repartidos en todos estos núcleos.

Igual que la microarquitectura Tremont, hereda en cierta medida lo que fueron en su día los núcleos Atom de Intel.

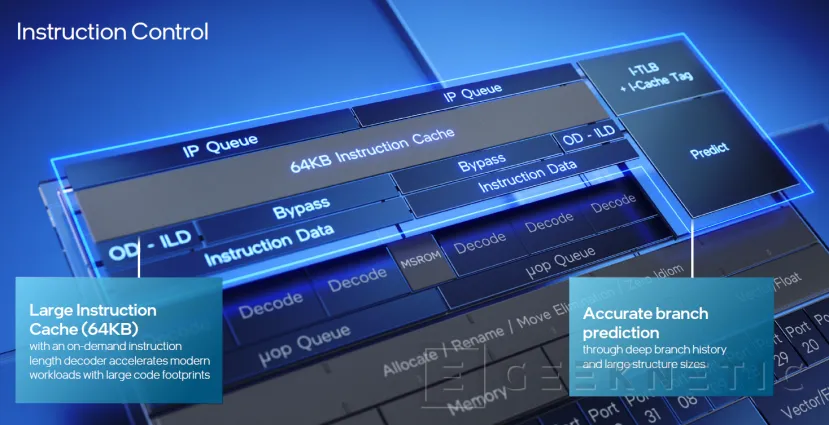

Control de Instrucciones

Como toda microarquitectura moderna, antes de la ejecución de un proceso se realiza un análisis de las instrucciones en cola a fin de predecir la forma más eficiente de ejecutarlas, moverlas o eliminarlas. De esto se ocupa la parte del núcleo dedicada al control de instrucciones.

Se caracteriza por disponer de un mejorado control de instrucciones con un predictor de saltos (Branch Predictor) renovado que, según Intel es más eficaz. Un buen Branch Predictor es sin duda una parte fundamental de CPUs modernas, ya que permite a la CPU predecir qué instrucciones deben ejecutarse de una forma u otra, en qué ciclo, en qué partes del núcleo, cuales se deben descartar y cuales se deben acomodar de una forma más eficiente en el hilo de proceso.

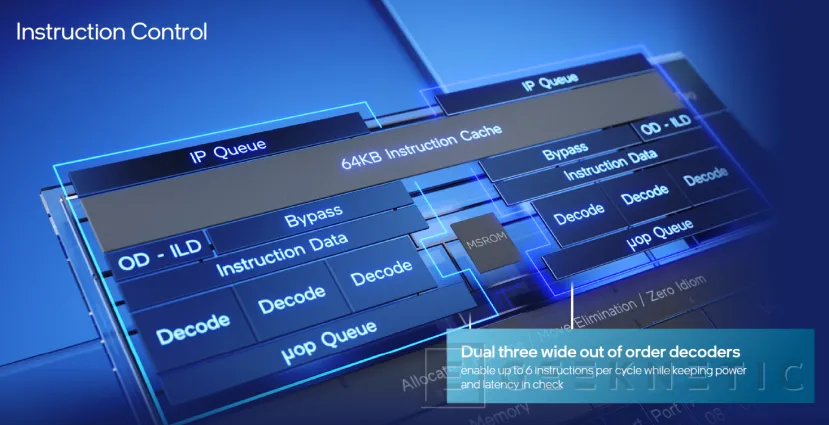

Dispone de una caché L1 de instrucciones de 64KB, con un decodificador adaptable bajo demanda que tiene la capacidad de soportar hilos de trabajo de gran envergadura. Es un decodificador dual capaz de trabajar con 6 instrucciones (3 por elemento decodificador) por ciclo al tiempo que tiene en cuenta la potencia y la latencia en su ejecución.

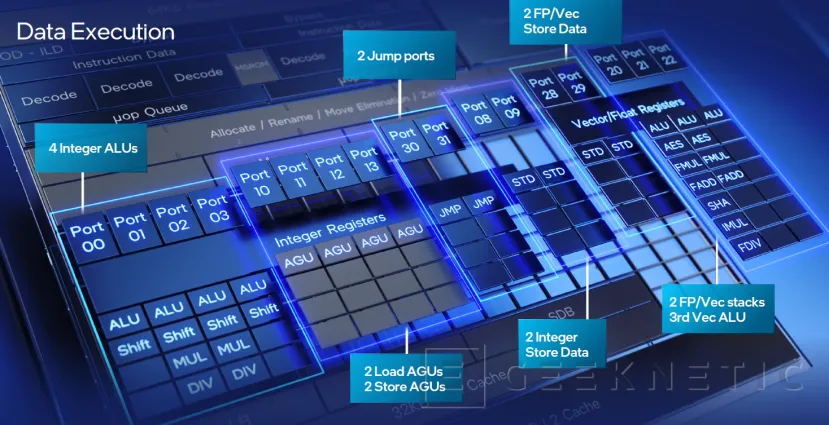

Ejecución de datos

Los núcleos Gracemont de los “Efficient Cores” disponen de 17 puertos destinados a la ejecución de instrucciones repartidos del siguiente modo:

- 4 están destinados a Unidades Aritméticas Lógicas (ALUs) de enteros

- 4 están destinadas a resolver direcciones de memoria, 2 para guardar y 2 para cargar

- 2 puertos destinados a ejecutar saltos en el hilo de instrucciones

- 2 puertos destinados a guardar datos de enteros

- 2 puertos destinados a almacenar datos de coma flotante o vectoriales.

- 3 puertos destinados a las pilas de coma flotante o vectoriales y las Unidades Aritméticas Lógica para vectores.

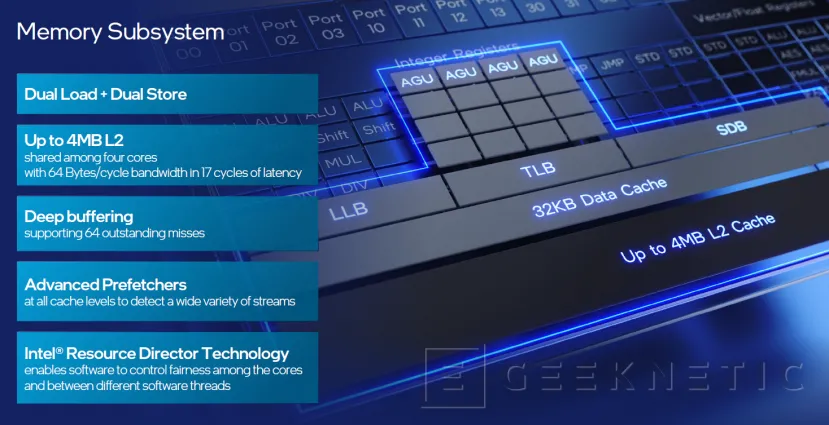

Sistema de Caché

Contamos con un sistema de caché L1 que consta de 32KB para datos y 64KB para instrucciones por núcleo tal y como se ha indicado en el apartado de control de instrucciones. Además permite realizar 2 operaciones de guardado y 2 operaciones de carga de forma simultánea por cada ciclo, 32 bytes para cada tipo de operación.

4MB en total tiene la cache L2 compartida que comparten cada conjunto de 4 núcleos. Tiene un ancho de banda de 64 Bytes por ciclo en 17 ciclos de latencia.

Dispone de un sistema de precarga de datos más profundo que soporta hasta 64 omisiones en la asignación a cada buffer y se introduce una nueva tecnología llamada “Intel Resource Director” que permite al software tener un mayor control sobre la equidad entre los recursos usados por cada uno de los núcleos y los hilos que se están procesando.

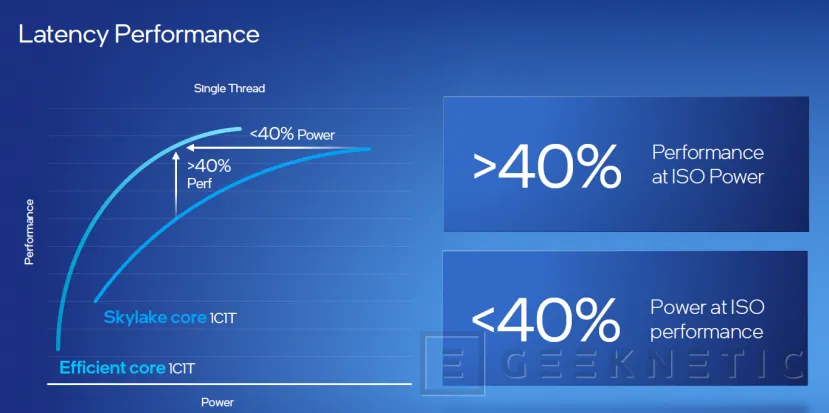

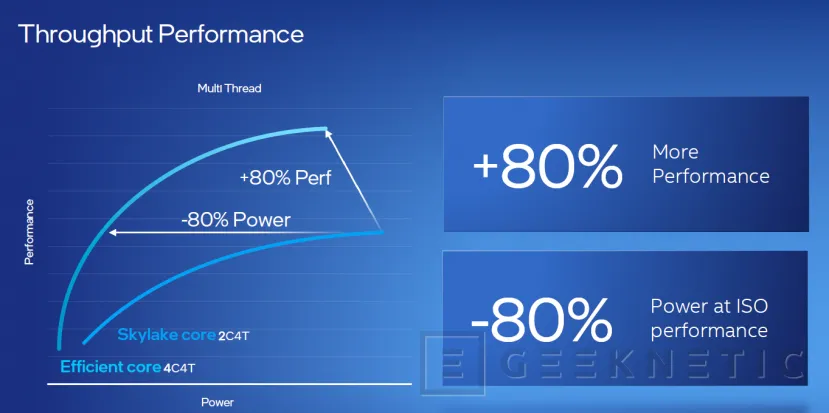

Rendimiento

Intel ha comparado el rendimiento por vatio de estos núcleos con respecto al rendimiento de los núcleos de su arquitectura Skylake.

Según Intel cuando comparamos los núcleos de 1 en 1 (y a 1 solo hilo por núcleo) estamos ante un 40% de más rendimiento a la misma potencia o bien un 40% menos de potencia necesaria para el mismo rendimiento.

Si lo escalamos a 4 hilos, usando los 4 núcleos en el caso de los Efficient Cores de Alder Lake, y 2 núcleos y 4 hilos (por HyperThreading) en Skylake, la diferencia es de hasta un 80%.

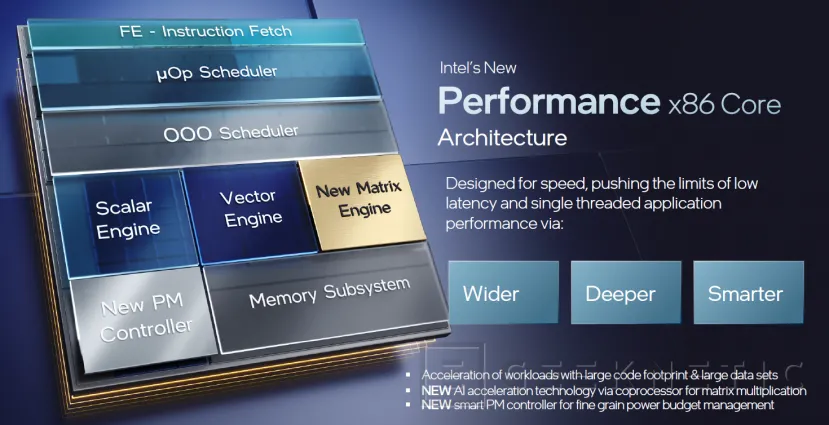

Intel Performance Core – Microarquitectura Golden Cove.

Los núcleos basados en esta microarquitectura que integran las CPUs Alder Lake son los destinados a entregarnos el máximo rendimiento en las circunstancias en que sea necesario. Estos núcleos sí que incorporan HyperThreading, permitiendo que se puedan ejecutar 2 hilos por núcleo de forma concurrente.

Heredan todo lo introducido en la microarquitectura Cypress Cove, que integran las CPUs Rocket Lake como el Intel Core i9-11900K, y mejoran ciertos aspectos que veremos a continuación.

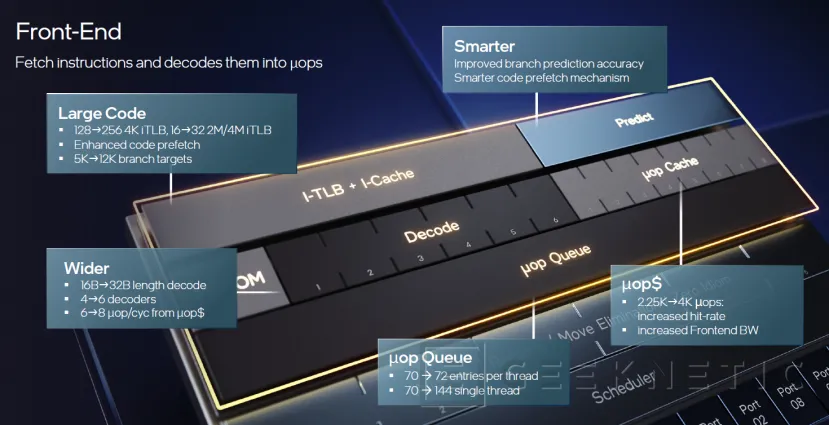

Control de Instrucciones

Según Intel, el predictor de saltos (Branch Predictor) que incorporan estos núcleos tiene un algoritmo mejorado que permite aumentar la precisión de las predicciones. Además, han aumentado la caché de entradas para el predictor de saltos hasta las 5.000, que se ve complementado con un largo historial de instrucciones ejecutadas a disposición de este, a fin de aumentar su eficacia.

Una gran ventaja de esto es que pueden anticiparse a problemas en las instrucciones como cuando la caché no está asignada correctamente y solucionarlo antes de que la instrucción llegue al punto en que es crítica su ejecución. Algunas de las tareas que más se benefician de esto son los navegadores de internet, las bases de datos y todo tipo de procesamiento de paquetes.

Cada núcleo cuenta con 6 decodificadores de instrucciones capaces de decodificar longitudes de 32 Bytes y permitiendo decodificar 8 micro operaciones por ciclo desde la caché de micro operaciones.

El decodificador de esta arquitectura cuenta además con un nuevo sistema bajo demanda que decodifica el tamaño de las instrucciones y genera información sobre las mismas que es almacenada junto a la caché de instrucciones. Esto permite que código que no haya sido visto antes sea decodificado con mayor rapidez. La siguiente vez en que se ejecuta esta misma instrucción se obvia el uso del decodificador de tamaño para no malgastar energía.

La caché de micro operaciones ha sido aumentada a 4 mil micro operaciones y la cola de micro operaciones es capaz de almacenar 72 entradas por hilo (en HyperThreading) o 144 en el caso de que el núcleo solo esté ejecutando 1 hilo.

Organización de Instrucciones y Ejecución

El motor de organizado de instrucciones se ha mejorado para permitir 12 puertos de ejecución, a diferencia de los 10 de que disponía Cypress Cove y consiguen que se ejecuten más instrucciones en la fase de renombrado / asignación / eliminación gracias a una interpretación más eficaz de las mismas por parte del Branch predictor.

Uno de los puertos adicionales va destinado a añadir una Unidad de Ejecución Aritmética (ALU) para enteros para un total de 5. También se dispone de la posibilidad de ejecutar la instrucción LEA, para computar la dirección absoluta de posiciones de memoria 1 vez por ciclo en cada uno de los 5 puertos destinados a cálculos de enteros con ALU.

En coma flotante o unidades de ejecución de vectores se ha mejorado el multiplicador binario FADD para mayor eficiencia y menor latencia. Ahora además las unidades de multiplicación FMA soportan datos en formato FP16. Los datos en formato FP16 han sido añadidos al conjunto de instrucciones AVX512 de Intel, incluyendo el soporte para números complejos.

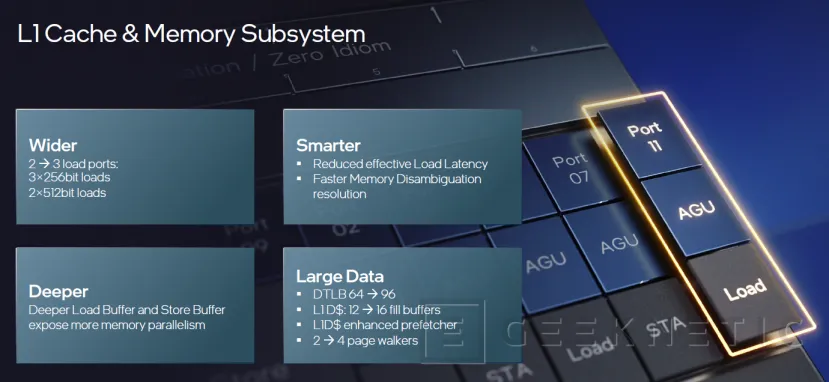

Sistema de Caché y Gestión de Memoria

La capacidad para cargar datos de la caché se ve sustancialmente mejorada. Han aumentado de 2 a 3 puertos de carga, permitiendo 3 cargas de 256bits o 2 cargas de 512bits. Los buffers de carga y de guardado han sido ampliados de forma que ahora reflejan mejor el paralelismo de la memoria.

Además, han conseguido reducir la latencia de carga de datos al tiempo que son capaces de cargar cantidades de datos más grandes por cada ciclo.

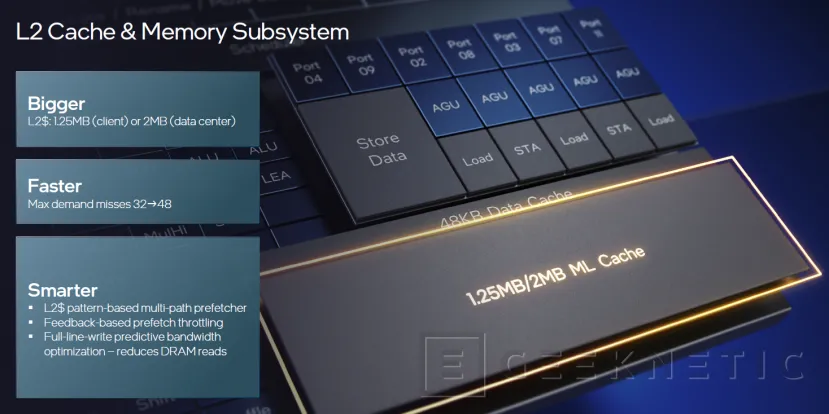

La caché L2 que tendremos a nuestra disposición son 1,25MB por núcleo en CPUs de consumo o 2MB las CPUs para servidor. Se incluyen otras mejoras como optimizaciones en las predicciones de ancho de banda para escrituras de línea completa, que tiene como resultado reducir el volumen de lecturas en la RAM.

Intel también ha destacado el nuevo motor de captura previa de datos de la caché que le permite entender mejor el comportamiento del programa en ejecución. La forma en que lo hace es observando el programa en curso y estimando cómo serán los próximos accesos a memoria. Puede detectar múltiples secuencias futuras de acceso a memoria y puede recolectar las direcciones de memoria con antelación.

Gestión de Energía

Intel ha implementado un microcontrolador de energía mejorado que analiza y captura eventos con una granularidad de microsegundos (en lugar de milisegundos). De esta forma le permite aumentar la precisión en el uso de energía basada en el comportamiento de la aplicación en curso. El resultado es una frecuencia de trabajo más alta para cualquier tipo de aplicación.

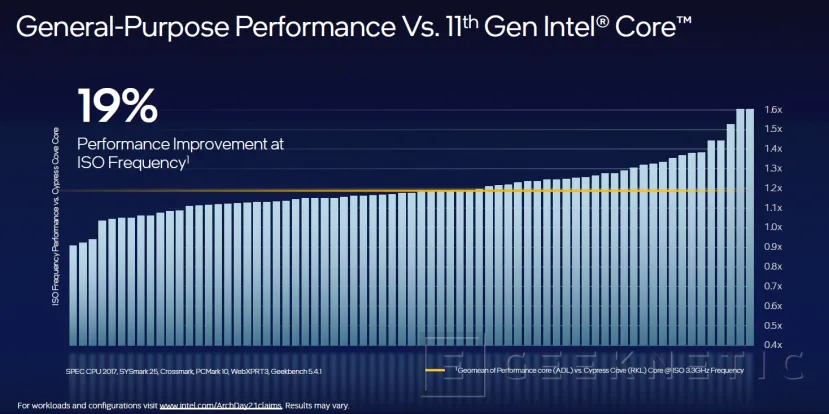

Rendimiento

Intel promete un 19% más de rendimiento, de media, con respecto a los núcleos Cypress Cove, según han visto en test en que han comparado ambos a una frecuencia fija 3,3GHz. Podemos asumir que estamos ante un 19% más de IPC, pero tendremos que esperar más datos para llegar a esa conclusión.

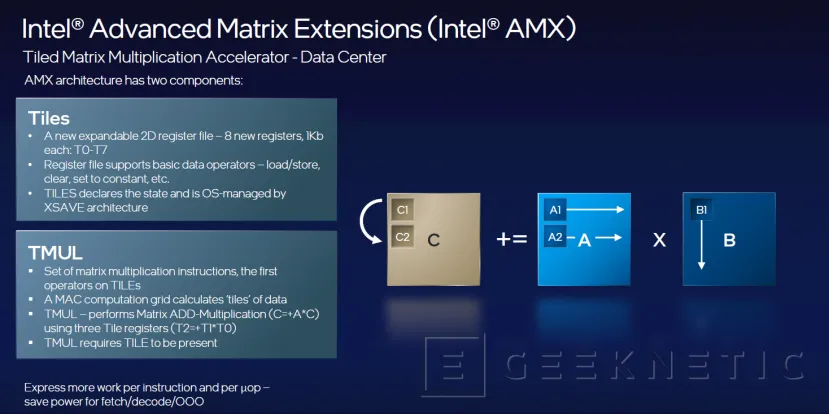

Intel AMX – Datacenters

Otra de las mejoras que incluirán estos núcleos, al menos en CPUs destinadas a servidores, es el Intel Advanced Matrix Extensions. Permite acelerar la multiplicación de matrices que es tan necesaria para la inteligencia en entornos de Machine Learning.

Intel Thread Director – Asignación de Hilos

El Sistema Operativo es el encargado de asignar los procesos a los distintos núcleos de la CPU según considera conveniente. Mientras todos los núcleos sean iguales esto no tiene una gran complejidad, Windows va asignando las tareas a los núcleos en función de la carga de cada núcleo y unos pocos factores más. El problema viene cuando introduces una CPU que tiene 2 tipos de núcleos muy distintos entre sí. Windows carece de la información necesaria para asignar los hilos de forma eficiente a cada tipo de núcleo según corresponda.

Para solucionar esto Intel ha creado una tecnología que llaman Thread Director. Es básicamente un elemento adicional incluido en la CPU que monitoriza los núcleos y los hilos de proceso y da información a Windows para ayudarle a que tome las decisiones de asignación de hilos correctas para mayor eficiencia y rendimiento, según sea necesario. Esto ocurre de forma dinámica y se producen saltos de hilos de unos tipos de núcleos a otros según el estado de cada hilo de trabajo.

Ejemplo de ejecución de tareas con Thread Director:

- Tenemos tareas prioritarias ejecutándose en los Performance Cores y otras tareas en segundo plano ejecutándose en los Efficient Cores.

- Ejecutamos una tarea de inferencia en IA.

- Se asigna la tarea a los Performance Cores.

- Tras un tiempo de ejecución intensiva llega un punto en el proceso de la tarea en el cual baja su actividad debido a que tiene que esperar a algo, ya sea interacción del usuario u otras cosas.

- El Thread Director detecta esto y envía la información al respecto Sistema Operativo.

- El Sistema Operativo toma la decisión de mover la tarea a los Efficient Cores.

- Una vez la tarea vuelve a iniciar su actividad de procesamiento intensiva el Thread Director lo detecta y envía la información al Sistema Operativo.

- El sistema operativo vuelve a mover el hilo a los Performance Cores.

Todo esto ocurre en milésimas de segundo, de forma totalmente automática y sin necesidad de que el usuario haga nada.

Según nos indica Intel, han trabajado con Microsoft para optimizar todo esto en Windows 11, y nos garantizan un funcionamiento óptimo bajo este sistema operativo. Por el momento desconocemos qué tal funcionará bajo Windows 10 u otros sistemas operativos. De todas formas, aunque Intel no ha mencionado nada al respecto, cabe esperar que el soporte y optimización se extienda a la inmensa mayoría de sistemas operativos incluyendo Unix/Linux, VMWare, BSD, Solaris, etc.

Implementaciones en Productos para usuario final

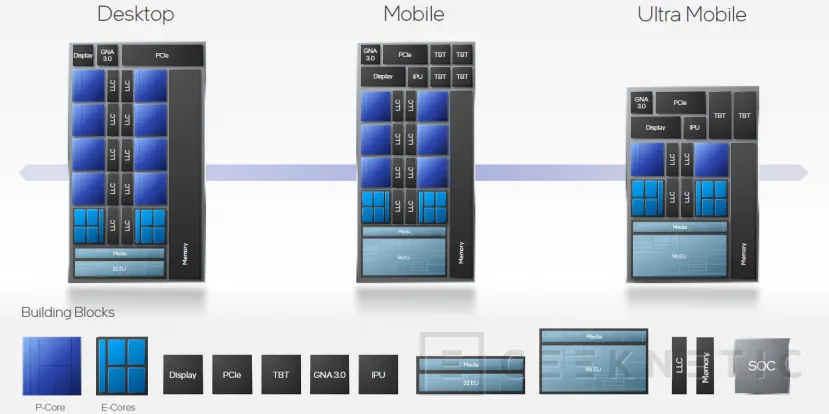

A nivel de consumo Intel ha detallado el uso de Alder Lake para 3 plataformas: Sobremesa con el socket LGA 1700, Portátiles de alto rendimiento con socket BGA Tipo 3 y portátiles de movilidad avanzada con el socket BGA Tipo4 HDI.

Aunque no han dado datos específicos podemos esperar que los TDPs de cada plataforma sean similares a los productos que sustituirán.

En la siguiente imagen podemos ver que la implementación en los distintos productos se hace por bloques que adaptan el producto a las necesidades.

Podemos observar que en CPUs para portátiles de alto rendimiento (el bloque del medio) se implementan 6 Performance Cores y 2 bloques de 4 Efficient Cores cada uno y sin embargo en las CPUs de portátil de bajo consumo o para alta movilidad tenemos 2 Performance Cores y 2 bloques con 4 Efficient Cores cada uno. Aunque no tenemos detalles de la configuración de productos finales para portátiles sí que podemos deducir que estos serán los máximos.

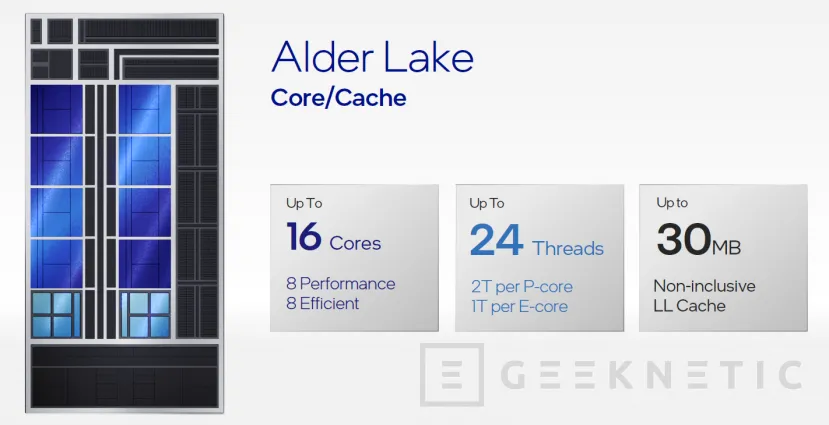

Intel también nos ha detallado el máximo que de núcleos que se soportan en Alder Lake, al menos en productos de consumo. Veremos CPUs con un máximo de 16 núcleos siendo 8 Performance Cores y 8 Efficient Cores. Teniendo en cuenta que solo los Performance Cores tienen HyperThreading estamos ante un total de 24 hilos. El máximo de memoria caché por CPU que veremos es de 30MB.

Podemos asumir por tanto que esta será la configuración exacta del tope de gama, al menos en sobremesa; el tan rumoreado Core i9-12900K (producto y nombre todavía sin confirmar por Intel) que estamos ansiosos por ver en acción.

Conclusiones: ¿Qué podemos esperar de Alder Lake?

Intel acaba de dar un gran giro en la forma en que plantean sus CPUs, que son la piedra angular de su negocio. Son los primeros en hacer un cambio radical en arquitecturas de PC hacia computación híbrida siguiendo los pasos de ARM y sus socios en otros segmentos.

En portátiles la llegada de los Efficient Cores es sin duda más que bienvenido y diría que necesario. Tiene sentido tener núcleos que trabajen aquellas cosas que no son tan intensivas de una forma más eficiente, con el ahorro energético que conlleva. Sin duda veremos grandes incrementos en la autonomía de los portátiles basados en Alder Lake y con toda seguridad tendrán menos dificultades para disipar el calor.

Qualcomm además ya tiene una plataforma que es capaz de hacer lo mismo, aunque su solución parte de arquitecturas pensadas inicialmente para móviles y tablets. No obstante la arquitectura ARM big.LITTLE de sus Snapdragon para Windows ha demostrado que pueden alcanzar el rendimiento de portátiles convencionales en combinación a 20 horas de autonomía. Esa gran autonomía es sin duda un plato muy apetecible para Intel, que siempre ha dado gran importancia a crear soluciones que van en esa dirección, y de alguna forma habrá sido un extra de motivación hacia la creación de la arquitectura híbrida Alder Lake.

En sobremesa y sobre todo en CPUs destinadas al mercado gaming, la necesidad de usar Efficient Cores no parece tan evidente y hay un gran número de escépticos que dudan de su éxito. Sin embargo, seguiremos contando con los Performance Cores, que según Intel son un 19% más rápidos que los núcleos del Core i9-11900K de la generación anterior. Todo parece indicar que también tendremos 8 núcleos de alto rendimiento con capacidad para 16 hilos en las CPUs de mayor alta gama.

La llegada del DDR5 es más que esperada y bienvenida, aunque como pasa con todo nuevo interfaz de memoria cuando se introduce en sobremesa, puede que al principio no rinda tan bien como esperamos. Es probable que veamos placas base híbridas o placas base que solo soporten DDR4, especialmente al principio.

La implementación de PCIe de 5ª generación puede ser interesante para entornos de servidor, pero en productos de consumo es improbable que suponga una mejora sustancial. Tenemos que recordar que los productos de almacenamiento y las tarjetas gráficas actuales todavía no son capaces de aprovechar todo el potencial del PCIe de 4ª generación que no hace tanto que ha sido introducido.

Por el momento no tenemos especificaciones de producto finales, precios y fechas, pero si seguimos la tendencia de Intel en las últimas generaciones deberíamos esperar que los portátiles de bajo consumo y alta movilidad sean los primeros en implementar esta arquitectura.

Aunque la feria IFA Berlín ha sido cancelada este año debido al coronavirus, sí que se esperan lanzamientos de fabricantes de portátiles durante la primera semana de septiembre en que se habría celebrado. No sería la primera vez en que Intel aprovecha las fechas de la feria para sacar productos basados en sus nuevas arquitecturas.

En caso de que no sea en estas fechas, Intel tiene preparado un evento online que llaman Intel Innovation que se llevará a cabo los días 27 y 28 de octubre. Sin no sabemos más para entonces esperamos que esa sea la fecha en que acaben de desvelar todos los detalles de los productos basados en esta arquitectura, sean para portátil o sobremesa.

¿Qué opinas de la llegada de la computación híbrida a los PCs? ¿Crees que será un acierto? ¿Crees que pondrá en apuros a AMD en algunos de los segmentos? Cuéntanoslo más abajo en los comentarios.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!